반도체 성능 향상의 역사에서 ‘패키징’의 변화는 제조 공정의 변화만큼이나 시대의 변화를 이끌어 왔다. 그리고 인텔은 최신 제조공정과 ‘패키징’ 기술을 결합해 지속적인 ‘무어의 법칙’을 달성하며 구현 가능한 최선의 성능 향상을 지속적으로 이뤄왔다.

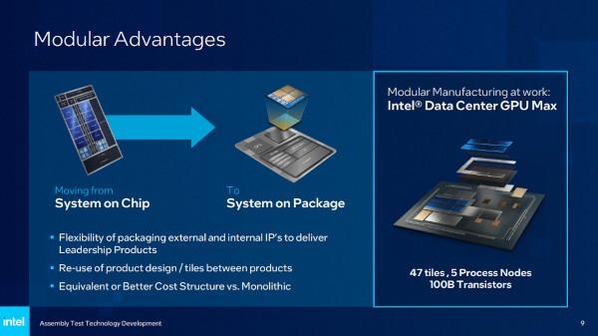

인텔은 18일 온라인 브리핑을 통해 향후 인텔이 선보일 주요 패키징 기술의 로드맵 정보를 공유했다. 이 자리에서 인텔은 기존의 EMIB(Embedded Multi-Die Interconnect Bridge)와 포베로스(Foveros) 기술의 핀 피치를 줄이고 밀도를 높일 예정이며, 패키징 결합 가능한 물리적 크기 또한 더욱 확장할 것이라고 강조했다.

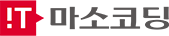

인텔의 EMIB나 포베로스 기술은 이미 인텔의 주요 제품군에서 활용되고 있다. 특히 ‘인텔 데이터센터 GPU 맥스 시리즈’는 EMIB와 포베로스 등의 기술을 모두 사용해 5개의 제조 공정으로 만들어진 47개의 타일을 하나의 제품으로 결합했다. 인텔은 현재 뿐 아니라 향후에 선보일 패키징 기술과 생태계를 인텔의 제품 뿐 아니라, 인텔의 파운드리 서비스를 사용하는 고객들에게도 활용할 수 있게 제공할 계획이다.

이에 최근 반도체 업계 전반에서는 여러 개의 실리콘 다이를 연결해 하나의 제품처럼 구현하는 칩렛(Chiplet), 멀티칩 패키징 등의 기술을 주목하고 있다. 하나의 ‘빅 칩’ 대신 여러 개의 작은 칩을 상호 연결하면 생산에서의 부담을 줄이고 제품군을 다양화하는 등에서 다양한 장점을 기대할 수 있다.

이는 이미 1965년 고든 무어가 발표한 논문에서도 언급된 바 있는데, 고든 무어는 이미 이 시점에서부터 패키징의 중요성을 예측한 것으로 알려졌다. 이 논문에서 고든 무어는 "개별적으로 패키징되고 상호 연결된 작은 기능들로 대규모 시스템을 구축하는 것이 더 경제적일 수 있다"고 언급한 바 있다.

패키징 기술의 발달로 점점 더 많은 것들이 프로세서 패키지에 포함되고 있다. 지금까지의 인텔의 역사에서도 몇 번의 계기가 있었다. 80486 프로세서에는 업계 최초로 다이에 처음으로 캐시 메모리를 탑재했고, 2005년 ‘펜티엄 D’는 패키지 안에 두 개의 프로세서 다이를 탑재한 ‘멀티칩 패키징’을 선보였다. 2013년 모바일용 4세대 코어 프로세서에서는 프로세서 패키지 안에 PCH(Platform Controller Hub)를 통합하기도 했다.

패키징 기술의 발전은 평면 확장 뿐 아니라, 수직 방향으로의 ‘3D’ 확장도 이뤄지고 있다. 인텔의 ‘포베로스’ 기술이 이러한 수직 적층을 위한 기술이며, 2020년 선보인 ‘레이크필드(Lakefield)’를 통해 상용화됐다. 그리고, 인텔의 제품 중 가장 복잡한 패키징 기술을 사용하는 ‘인텔 데이터센터 GPU 맥스 시리즈’는 EMIB와 포베로스 등의 기술을 모두 사용해 5개의 제조 공정으로 만들어진 47개의 타일을 하나의 제품으로 결합했다.

인텔은 패키징 기술 중 멀티 다이의 단일 패키징 구성 등에 활용되는 100μm 급 FCBGA, FCLGA 기술에서는 기존의 92x92mm 크기보다 더 큰 100x100mm를 지원할 것이라고 소개했다. 메탈 레이어 지원 또한 26레이어로 늘어난다. 2022년까지 FCBGA 패키징 기술이 56x100mm, 24 메탈 레이어 지원이었음을 고려하면 큰 폭으로 확장된 것이다.

2.5D 패키징 기술인 EMIB에서는 범프 피치를 기존 55μm에서 45μm 수준으로 줄일 계획이다. 브릿지로의 전력 공급 개선 및 고대역폭 메모리(HBM) 연결 지원에 도움이 되는 TSV 지원도 검토하고 있다고 소개했다. 45μm 피치는 2024년, TSV 지원 45μm 피치는 2026년 정도에 등장할 예정이다. 사용 가능한 다이 사이즈 제약 또한 향후 면당 100mm 이상의 대형 패키지까지 제공할 수 있게 할 예정이다.

포베로스 기술 또한 범프 피치를 기존 36μm에서 25μm까지 줄여 나갈 계획이며, 2024년 등장할 예정이다. 칩간 결합에서 구리와 구리를 직접 본딩해 고밀도 저저항 인터커넥트를 구현하는 하이브리드 본딩 기술인 ‘포베로스 다이렉트(Foveros Direct)’는 범프 피치 10μm 이하의 기술이 2024년에 양산 준비될 예정이고, 5μm까지 빠르게 확장할 계획이라 언급했다.

한편, 인텔은 차세대 인터커넥트 구현 측면에서 2020년 후반대에 ‘유리 석영 기판(Glass Core Substrate)’을 도입할 계획이다. 이를 통해 전력 공급 개선과 고속 입출력(I/O) 구현을 위한 성능 향상이 기대된다고 밝혔다.

또한 패키지 수준에 통합된 광학 연결 기술로 뛰어난 성능의 연결성을 낮은 비용으로 얻을 수 있을 것이라 소개했다. 이 광학 연결 기술은 패키지상 광학 칩에 플러그 또는 분리 가능한 유리 기반 커플러가 활용될 계획이다. 새로운 기술은 USB-C 커넥터 크기의 플러그형 연결로 광케이블을 실리콘에서 분리할 수 있는 것이 특징이다. 인텔은 올해 하반기에 샘플 제공이, 2024년 말까지 제품 도입 가능한 수준의 품질 확보가 가능할 것으로 예상했다.

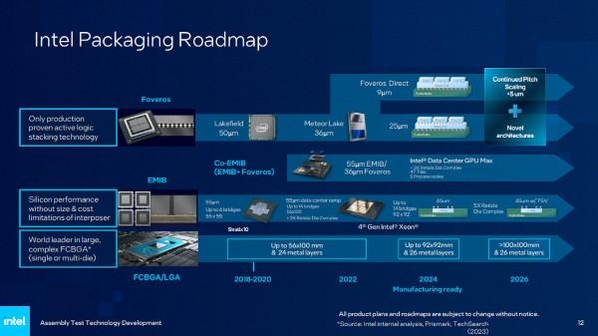

또한 인텔은 다양한 IP 공급 업체와 설계 지원, 시제품 공급과 파트너에 이르기까지 최적의 구성 요소들을 조합할 수 있는 생태계 구축이 중요하다고 강조했다. 특히, 다양한 공정의 활용이나 타사 파운드리 자원의 동시 활용에 이르기까지 다양한 상황에서의 유연성을 제공할 수 있어야 한다고 강조했다.

인텔은 파운드리 서비스에서 다양한 고객의 요구에 대응할 수 있는 비즈니스 모델을 갖추고 있다. 특히 제품 스펙에서 최종 설계까지, 설계와 웨이퍼 제조에서 패키징과 제조 선별 테스트까지 다양한 영역에서 인텔의 서비스와 다른 파운드리 서비스에서 제공하는 서비스를 결합할 수 있다. 예를 들면, 다른 파운드리 제조사에서 만든 웨이퍼로 인텔의 패키징 서비스만 사용하는 경우도 가능하다.

조립 및 테스트 네트워크 또한 인텔의 강점으로 꼽힌다. 인텔은 파운드리에 구애받지 않는 세트 서비스를 제공하고 있으며, 인텔 뿐 아니라 외부 파운드리의 웨이퍼를 사용하더라도 웨이퍼 선별이나 패키징 제조 공정 등에서 지금까지 축적된 높은 전문 역량을 제공한다고 강조했다. 또한 연구개발과 제조 부문에서 여러 대륙에 걸쳐 시설을 운영하고 있으며, 유연한 공급망을 통한 고객 지원이 가능하다고 덧붙였다.

권용만 기자 yongman.kwon@chosunbiz.com